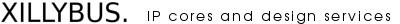

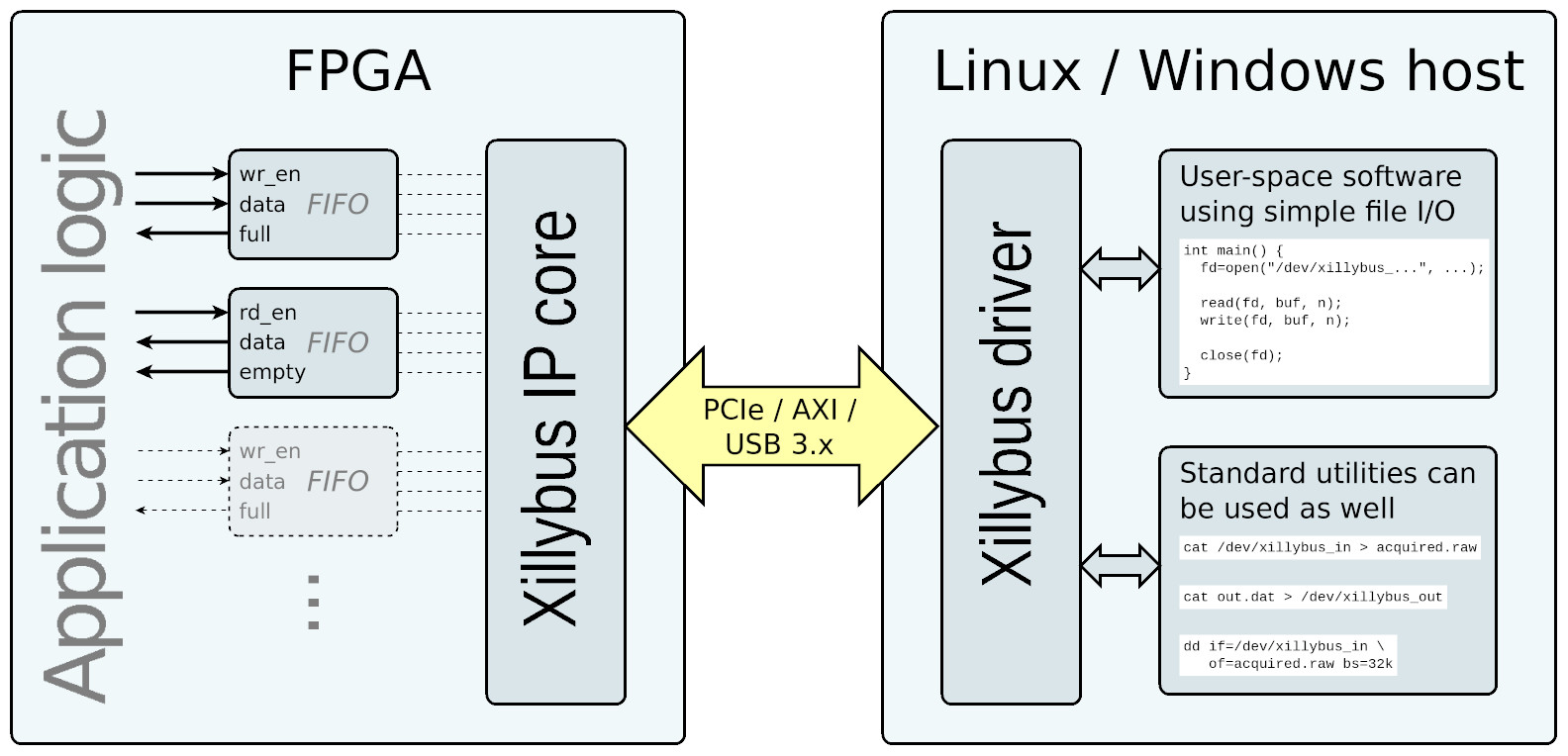

Xillybus and XillyUSBConnecting an FPGA with a Linux / Windows host through a PCIe, AXI or SuperSpeed USB bus. | | Xillyp2pConnecting two FPGAs through a Multi-Gigabit transceiver (MGT) or simpler I/O (serial / parallel wires between two FPGAs). |

Features- Minimal effort for setting up the data exchange link, cutting development risk, cost and schedule dramatically

- An FPGA IP core and a driver for the host create an illusion of a continuous data stream between a FIFO and a file on the host

- No low-level design or driver programming

- FPGA designers interface with the IP core through a standard FIFO or dual-port memory

- Simple API: Application software written in userspace, using simple streaming file I/O

- DMA used exclusively for data transfers, hence minimal load on processor

- Low latency

- A custom IP core automatically generated according to configuration. Up to 160 FIFOs sharing a single PCIe link

- Driver for Linux included in mainstream Linux distributions

- Driver for Windows 7 and later available for download

- Portability: Seamless transition between AMD and Altera FPGAs, Linux and Windows

- Works on any host with PCIe and/or USB 3.x: Common PC computers, PC-on-board (PCI/104-Express) and embedded processors (e.g. NXP's i.MX series, and Nvidia Jetson / Tegra)

| Applications- Data acquisition

- Video capture and playback

- Hardware acceleration

- FPGA control from host

- Easy design of peripherals

- Interface with dedicated hardware

- Logic verification on hardware

- Fast development of dedicated lab equipment

- Debugging

More informationTry it out!

Try Xillybus with your application data from the FPGA to the host and vice versa. It's not just a demo, it works for real. Connect your application data to a standard FIFO, boot the computer or FPGA with either Windows or Linux, and see how easy it is to talk with your FPGA!

Very fast setup: A day or two is the typical lead time from downloading core & drivers to an end-to-end integration between host application and dedicated logic on FPGA. | Features- Comprehensive and complete solution for a point-to-point connection through an MGT or other serial / parallel I/O, cutting development risk, cost and schedule dramatically

- Data rates: 10 Mbit/s to physical link's limit

- Mulitple independent communication channels, per custom configuration.

- Simple and intuitive interface: Each communication channel behaves like a FIFO spanning across the two FPGAs

- Flow control fully implemented by the IP core, based upon respecting the receiving FIFO's "full" port.

- Reliable data handling: Error detection and automatic retransmission

- Optional End-of-Packet port allows dividing data stream into packets

- Simple setup of MGT: Only SERDES functionality required. All synchronization needs and clock frequency compesation are implemented inside the IP core

- Hotpluggable

- 97% bandwidth efficiency (application data rate to physical link's data rate, typical at BER=0). Raw bandwidth is divided among the application channels for low latency and optimal performance

- Data on physical link is randomized with a scrambler, allowing equalizer

- Automatic compensation for negated bit polarity

- Built-in optional bit error injection for testing

- Unidirectional physical link supported (albeit without flow control or automatic retransmission)

| Applications- Connection between several FPGAs on the same board

- Connection between FPGAs through a backplane.

- Data acquisition with a remotely located FPGA

- Data output to a remote facility

- Long-distance data transport using optical fiber

- Electrical isolation (using optical fiber)

- Data link with peripheral equipment through a cable (cameras, displays, sensors, radio transceivers etc.)

- Cost reduction of I/O-intensive applications

More informationTry it out!Try Xillyp2p with your application data. It's not just a demo, it works for real. Xillyp2p is easy to integrate with an MGT or with general-purpose FPGA I/O. Refer to Xillyp2p's main page for a complete design example of setting up an GTX / GTH for a optical fiber connection between two development boards, including the complete setup of the MGT block, instantiation of this block as well as the Xillyp2p IP core and constraints. |