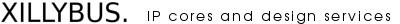

Start with the demo bundle...

The Xillybus IP core currently supports the PCIe target for Windows, and three targets for Linux, as listed below. Even though the Xillybus devices behave the same, the bundles for each target are completely different.

Please choose one of the four:

- Xillybus for PCIe: Windows or Linux runs on a plain PC, FPGA contains the peripheral interface only. Data transport is PCI Express.

- XillyUSB, based upon USB 3.0: Like Xillybus for PCIe, but an USB 3.0 cable connects between the Linux host and the FPGA, which behaves as a USB device.

- Xillinux for Zynq-7000: A full Linux distribution, including the Xillybus IP core and drivers, for running the a complete graphical desktop in the platform.

- Xillybus for Microblaze (phased out): Linux runs on a Microblaze processor on the FPGA, which also contains the peripheral interface. Data transport is the processor's AXI4 bus.

For the Xillyp2p IP core, please refer to its own start page. This IP core's work flow is slightly different from the diagram shown to the right.

... and then configure & download your own custom IP core

After getting the demo bundle up and running, and the principles are understood, go to the IP Core Factory and set up a Xillybus IP core according to your own needs.

The suggested general flow is depicted to the right.