# Xillybus host application programming guide for Windows

|   |       | Xillybus<br>www.xillybus.c                                          |     |

|---|-------|---------------------------------------------------------------------|-----|

|   |       | Version                                                             | 3.0 |

| 1 | Intro | oduction                                                            | 4   |

| 2 | Syn   | chronous streams vs. asynchronous streams                           | 5   |

|   | 2.1   | Overview                                                            | 5   |

|   | 2.2   | Motivation for asynchronous streams                                 | 6   |

|   | 2.3   | Streams from FPGA to host                                           | 6   |

|   | 2.4   | Streams from host to FPGA                                           | 7   |

|   | 2.5   | Uncertainty vs. latency                                             | 8   |

| 3 | I/O   | programming practices                                               | 10  |

|   | 3.1   | Overview                                                            | 10  |

|   | 3.2   | Guidelines for reading data                                         | 11  |

|   | 3.3   | Guidelines for writing data                                         | 14  |

|   | 3.4   | Performing flush on asynchronous downstreams                        | 16  |

|   | 3.5   | Using Microsoft's native API                                        | 18  |

|   | 3.6   | Monitoring the amount of data in driver's buffers                   | 20  |

|   | 3.7   | XillyUSB: The need to monitor the quality of the physical data link | 20  |

| 4 | Con   | tinuous I/O at high rate                                            | 22  |

|   | 4.1   | The basics                                                          | 22  |

|   | 4.2                                                                                      | Large driver's buffers                                                                                                                                                                                                                                                                                                                                |  |  |  |  |

|---|------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

|   | 4.3                                                                                      | RAM buffers in user space                                                                                                                                                                                                                                                                                                                             |  |  |  |  |

|   | 4.4                                                                                      | Why not just Windows pipes?                                                                                                                                                                                                                                                                                                                           |  |  |  |  |

|   | 4.5                                                                                      | Overview of the fifo.c demo application                                                                                                                                                                                                                                                                                                               |  |  |  |  |

|   | 4.6                                                                                      | fifo.c modification notes                                                                                                                                                                                                                                                                                                                             |  |  |  |  |

|   | 4.7                                                                                      | RAM FIFO functions                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |

|   |                                                                                          | 4.7.1 fifo_init()                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |

|   |                                                                                          | 4.7.2 fifo_destroy()                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |

|   |                                                                                          | 4.7.3 fifo_request_drain()                                                                                                                                                                                                                                                                                                                            |  |  |  |  |

|   |                                                                                          | 4.7.4 fifo_drained()                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |

|   |                                                                                          | 4.7.5 fifo_request_write()                                                                                                                                                                                                                                                                                                                            |  |  |  |  |

|   |                                                                                          | 4.7.6 fifo_wrote()                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |

|   |                                                                                          | 4.7.7 fifo_done()                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |

|   |                                                                                          | 4.7.8 The FIFO_BACKOFF define variable                                                                                                                                                                                                                                                                                                                |  |  |  |  |

| 5 | Cvc                                                                                      | lic frame buffers 3                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |

|   | 5.1                                                                                      | Introduction                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |

|   |                                                                                          |                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |

|   | 5.2                                                                                      | Adapting the FIFO example code                                                                                                                                                                                                                                                                                                                        |  |  |  |  |

|   | 5.2<br>5.3                                                                               | Adapting the FIFO example code       32         Dropping and repeating frames       34                                                                                                                                                                                                                                                                |  |  |  |  |

|   | 5.3                                                                                      | Dropping and repeating frames                                                                                                                                                                                                                                                                                                                         |  |  |  |  |

| 6 | 5.3<br><b>Spe</b>                                                                        | Dropping and repeating frames    34      cific programming techniques    34                                                                                                                                                                                                                                                                           |  |  |  |  |

| 6 | 5.3                                                                                      | Dropping and repeating frames       34         cific programming techniques       38         Seekable streams       38                                                                                                                                                                                                                                |  |  |  |  |

| 6 | 5.3<br><b>Spe</b>                                                                        | Dropping and repeating frames       34         cific programming techniques       38         Seekable streams       38         Synchronizing streams in both directions       37                                                                                                                                                                      |  |  |  |  |

| 6 | 5.3<br><b>Spe</b><br>6.1                                                                 | Dropping and repeating frames       34         cific programming techniques       38         Seekable streams       38                                                                                                                                                                                                                                |  |  |  |  |

| 6 | <ul><li>5.3</li><li>Spe</li><li>6.1</li><li>6.2</li></ul>                                | Dropping and repeating frames       34         cific programming techniques       38         Seekable streams       38         Synchronizing streams in both directions       37                                                                                                                                                                      |  |  |  |  |

| 6 | <ul> <li>5.3</li> <li>Spe</li> <li>6.1</li> <li>6.2</li> <li>6.3</li> <li>6.4</li> </ul> | Dropping and repeating frames       34         cific programming techniques       38         Seekable streams       38         Synchronizing streams in both directions       37         Packet communication       38                                                                                                                                |  |  |  |  |

| 6 | 5.3<br><b>Spe</b><br>6.1<br>6.2<br>6.3<br>6.4<br>6.5                                     | Dropping and repeating frames       34         cific programming techniques       38         Seekable streams       38         Synchronizing streams in both directions       37         Packet communication       38         Emulating hardware interrupts       39                                                                                 |  |  |  |  |

| _ | 5.3<br><b>Spe</b><br>6.1<br>6.2<br>6.3<br>6.4<br>6.5<br><b>Hibe</b>                      | Dropping and repeating frames       34         cific programming techniques       33         Seekable streams       34         Synchronizing streams in both directions       37         Packet communication       38         Emulating hardware interrupts       39         Coprocessing / Hardware acceleration       39         ernation       42 |  |  |  |  |

| 7 | 5.3<br><b>Spe</b><br>6.1<br>6.2<br>6.3<br>6.4<br>6.5<br><b>Hibe</b>                      | Dropping and repeating frames       34         cific programming techniques       33         Seekable streams       34         Synchronizing streams in both directions       33         Packet communication       34         Emulating hardware interrupts       34         Coprocessing / Hardware acceleration       34         ernation       44 |  |  |  |  |

| A.2 | "Class  | ic" DMA vs. Xillybus                                 | 44 |

|-----|---------|------------------------------------------------------|----|

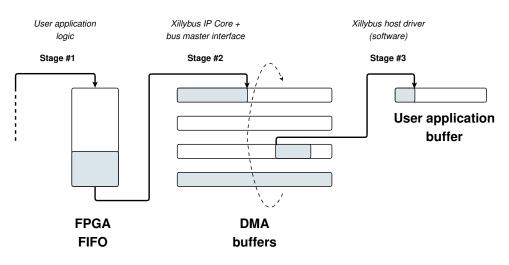

| A.3 | FPGA    | to host (upstream)                                   | 45 |

|     | A.3.1   | Overview                                             | 45 |

|     | A.3.2   | Stage #1: Application logic to intermediate FIFO     | 46 |

|     | A.3.3   | Stage #2: Intermediate FIFO to DMA buffer            | 46 |

|     | A.3.4   | Stage #3: DMA buffer to user software application    | 47 |

|     | A.3.5   | Conditions for handing over partially filled buffers | 48 |

|     | A.3.6   | Examples                                             | 49 |

|     | A.3.7   | Practical conclusions                                | 50 |

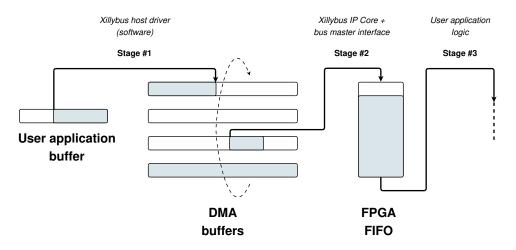

| A.4 | Host to | p FPGA (downstream)                                  | 51 |

|     | A.4.1   | Overview                                             | 51 |

|     | A.4.2   | Stage #1: User software application to DMA buffer    | 52 |

|     | A.4.3   | Stage #2: DMA buffer to Intermediate FIFO            | 53 |

|     | A.4.4   | Stage #3: Intermediate FIFO to application logic     | 53 |

|     | A.4.5   | An example                                           | 54 |

|     | A.4.6   | Practical conclusions                                | 54 |

|     |         |                                                      |    |

# Introduction

Xillybus was designed to present the Windows host with a simple and well-known interface, having a natural and expected behavior. The host driver generates system objects which behave like named pipes, and declare themselves as such. They are opened, read from and written to just like any file, but behave much like pipes between processes or TCP/IP streams. To the program running on the host, the difference is that the other side of the stream is not another process (over the network or on the same computer), but a FIFO in the FPGA. Just like a TCP/IP stream, the Xillybus stream is designed to work well with high-rate data transfers as well single bytes arriving or sent occasionally.

Since the interface with Xillybus is all through objects that are accessed like just any file, typically any practical programming language can be used, with no need for a special module, extension or any other adaption. If a file can be opened with the chosen language, it can be used to access the FPGA through Xillybus.

One driver binary supports any Xillybus IP core configuration: The streams and their attributes are auto-detected by the driver as initializes the device, and device files are created accordingly. These device files are accessed as \\.\xillybus\_something (or \\.\xillyusb\_00\_something with XillyUSB).

During operation, a handshake protocol between the FPGA and host makes an illusion of a continuous data stream. Behind the scenes, the driver's buffers are filled and processed. Techniques similar to those used for TCP/IP streaming are used to ensure an efficient utilization of the buffers, while maintaining responsiveness for small pieces of data.

# 2

# Synchronous streams vs. asynchronous streams

# 2.1 Overview

Each Xillybus stream has a flag, which determines whether it behaves synchronously or asynchronously. This flag's value is fixed in the FPGA's logic.

When a stream is marked asynchronous, it's allowed to communicate data between the FPGA and the host's kernel driver without the user space software's involvement, as long as the respective device file is open.

Asynchronous streams have better performance, in particular when the data flow is continuous. Synchronous streams are easier to handle, and are the preferred choice when tight synchronization is needed between the actions of the user space application and what happens in the FPGA.

In custom IP cores that are generated in the IP Core Factory, the selection between making each stream synchronous or asynchronous is automatically based upon the information about the stream's intended use, as declared by the tool's user when "autoset internals" is enabled. If the autoset option is turned off, the user makes this choice explicitly.

Either way, the "readme" file, included in the bundle that is downloaded from the IP Core Factory, specifies the synchronous or asynchronous flag for each stream (among other attributes).

In all demo bundles, the streams related to xillybus\_read\_\* and xillybus\_write\_\* are asynchronous. xillybus\_mem\_8 is seekable and therefore synchronous. When XillyUSB is used, the same applies to the respective xillyusb\_\* files.

## 2.2 Motivation for asynchronous streams

Multitasking operating systems such as Linux and Microsoft Windows are based upon CPU time sharing: Processes get time slices of the CPU, with some scheduling algorithm deciding which process gets the CPU at any given moment.

Even though there's a possibility to set priorities for processes, there is no guarantee that a process will run continuously, or that the periods of preemption have a limited duration, not even on a multiprocessor computer. The underlying assumption of the operating system is that any process can accept any period of CPU starvation. Real-time oriented applications (e.g. sound applications and video players) have no definite solution to this problem. Instead, they rely on the typical de-facto behavior of the operating system, and make up for the preemption periods with I/O buffering.

Asynchronous streams tackle this issue by allowing a data to flow continuously while the application is either preempted or busy with other tasks. The exact significance of this for streams in either direction is discussed next.

# 2.3 Streams from FPGA to host

In the upstream direction (FPGA to host), if the stream is asynchronous, the IP core in the FPGA attempts to fill the host driver's buffers whenever possible. That is, when the file is open, data is available and there is free space in those buffers.

On the other hand, if the stream is synchronous, the IP core fetches data from the user application logic (usually from a FIFO) only when the user application software on the host has a pending request to read that data from the file descriptor. In other words, when the user application software is in the middle of a read() function call.

Synchronous streams should be avoided in high-bandwidth applications, mainly for these two reasons:

- The data flow is interrupted while the application is preempted or doing something else, so the physical channel remains unutilized during certain time periods. In most cases, this leads to a significant bandwidth performance reduction.

- An overflow may occur on the FIFO in the FPGA during these time gaps. For example, if its fill rate is 100 MB/sec, a typical FPGA FIFO with 2 kByte goes from empty to full in around 0.02 ms. Practically, this means that any preemption of the user space program can potentially cause the overflow of the FIFO in the FPGA.

Despite these drawbacks, synchronous streams are useful when the time at which the data was collected at the FPGA is important. In particular, memory-like interfaces require a synchronous interface.

Data that has been received by the Xillybus IP core on the FPGA from the application logic is available for reading immediately by the host's user space application, regardless of whether the stream is synchronous or asynchronous.

## 2.4 Streams from host to FPGA

In the downstream direction (host to FPGA), a stream being asynchronous means that the host application's write() function calls will return immediately most of the time. More precisely, the calls to functions writing to the device file will return immediately if the data can be stored entirely in the driver's buffers. The data is then transmitted to the FPGA at the rate requested by the user application logic at the FPGA, with no involvement of the host's application software.

There is a slight difference between XillyUSB and the other Xillybus IP cores, regarding how soon the data is sent to the FPGA, on behalf of an asynchronous streams to the FPGA.

For the IP cores that are based upon PCIe or AXI, data is sent to the FPGA only when one of these happen:

- The current DMA buffer is full (there are several buffers for each stream).

- A flush is requested explicitly on the device file by the application software (see paragraph 3.4)

- The file descriptor is being closed.

- A timer expires, forcing an automatic flush if nothing has been written to the stream for a specific amount of time (typically 10 ms).

With a XillyUSB stream, the data is sent virtually immediately. More precisely, the driver attempts to queue USB transfers of a fixed size (typically 64 kB), but a smaller transfer is queued if there is data for transmission, and there's no other transfer queued for the related stream. Therefore, for each stream, there is never more than one queued transfer with less than the fixed size, but there is always at least one transfer in progress as long as there is data for transmission. This results in an efficient use of USB transfers as well as quick response to short data segments.

All in all, asynchronous streams on all IP cores (XillyUSB and other Xillybus IP cores) behave roughly the same, with XillyUSB having a quicker response time on short segments of data (no 10 ms delay).

On the other hand, if the stream is synchronous, a call to the low-level function writing to the device file will not return until all data has reached the user application's logic in the FPGA. In a typical application, this means that when the function call to write() returns, it indicates that the data has arrived to the FIFO that is connected to the IP core in the FPGA.

#### **IMPORTANT:**

Higher-level I/O functions, such as fwrite(), involve a buffer layer created by the library functions. Hence fwrite() and similar functions may return before the data has arrived at the FPGA, even for synchronous streams.

Synchronous streams should be avoided in high-bandwidth applications, mainly for these two reasons:

- The data flow is interrupted while the application is preempted or doing something else, so the physical channel remains unutilized during certain time periods. In most cases, this leads to a significant bandwidth performance hit.

- An underflow may occur on the FIFO in the FPGA during these time gaps. For example, if its drain rate is 100 MB/sec, a typical FPGA FIFO with 2 kByte goes from full to empty in around 0.02 ms. Practically, this means that any preemption of the user space program can potentially cause the underflow of the FIFO in the FPGA.

Despite these drawbacks, synchronous streams are useful when it's important for the application to know that the data has arrived to the FPGA. This is the case when the stream is used to transmit commands that must be executed before some other operation takes place (e.g. configuration of the hardware).

#### 2.5 Uncertainty vs. latency

A common mistake it to require a low latency on asynchronous streams for the sake of synchronization between data. For example, if the application is a modem, there is usually a natural need to synchronize between received and transmitted samples. This often leads to a misconceived design, based upon the notion the uncertainty in the synchronization is necessarily smaller than the total latency. To keep the uncertainty low, the latency, and hence buffers, are made as small as possible, leading to an overall system with difficult real-time requirements.

With Xillybus, the synchronization is easily made perfect (at the level of a single sample), as explained in paragraph 6.2. The limitation on latency is therefore derived from the need to respond quickly to arriving data, if there is such a need.

For example, with a modem, the maximal latency has an impact on how quickly the application's data source responds to data that is sent to it. In a camera application, the host may program the camera to adjust the shutter speed to compensate for changing light conditions. Data that arrives with a larger latency slows down this control loop.

These are the real considerations that need to be taken, and still, they are usually significantly less stringent than those derived from the misunderstanding of mixing uncertainty with latency.

# 3

# I/O programming practices

# 3.1 Overview

Xillybus works properly with any programming language which is able to access files, and any API for accessing files is suitable.

In this guide there's an emphasis on the low-level classic C API, based upon functions such as \_open(), \_read(), \_write() and \_close(). These underscore-prefixed functions behave exactly like their non-underscored counterparts, (i.e. \_read() and read() is the same function). However a Microsoft compiler may issue a warning when the non-underscored functions are used.

The Microsoft API (i.e. CreateFile(), ReadFile() etc.) can be used as well (see paragraph 3.5), but it is mostly ignored in this guide here for these reasons:

- the extra features given by the Windows API are not necessary (even though this API supplies a more accurate error reporting).

- the classic C API is well known, simpler, and more easily adopted by programmers.

- the classic C API is not likely to be modified across different versions of Windows.

- the classic C API is makes the code portable.

The low-level set is chosen over other well-known sets (e.g. fopen(), fwrite(), fprintf() etc.) because the low-level API's functions have no extra layer of buffers. These buffers can have a positive effect on performance, but with them there's no control over the actual I/O operations.

This is less important when data is transmitted constantly and no direct relation is expected between software operations and the I/O with the hardware.

An extra buffer layer can also cause confusion, making it look like there's a software bug where there isn't. For example, a function call to fwrite() can merely store the data in a RAM buffer without performing any I/O operation until the file is closed. A developer not aware of this may be mislead to think that the fwrite() failed because nothing happened on the FPGA side, when in fact the data is waiting in the buffer.

This section describes the recommended UNIX programming practices, using the lowlevel C run-time library functions. This elaboration is given here for the sake of completeness, as there is nothing specific to Xillybus about any of these practices.

The code snippets are taken from the demo applications described in Getting started with Xillybus on a Windows host. The device file names in these examples are those of the Xillybus IP core for PCIe.

The examples below are given for the PCIe variant of Xillybus. They apply to XillyUSB as well, however the file name prefix is xillyusb\_00\_\* instead of xillybus\_\*. If there are multiple XillyUSB devices connected, the "00" part is replaced with the lowest index that was free when the device was discovered, i.e. 01, 02 etc. Once a device is assigned an index, it doesn't change as long as it remains connected.

The typical header files for these examples are

```

#include <io.h>

#include <stdio.h>

#include <stdlib.h>

#include <errno.h>

#include <sys/types.h>

#include <sys/stat.h>

#include <fcntl.h>

```

## 3.2 Guidelines for reading data

Assuming that the variables have been declared as follows:

```

int fd, rc;

unsigned char *buf;

```

The device file is opened with the low-level open (the file descriptor is in integer format):

```

fd = _open("\\\.\\xillybus_ourdevice", O_RDONLY | _O_BINARY);

if (fd < 0) {

perror("Failed to open devfile");

exit(1);

}</pre>

```

The  $\\\$  prefix in the file name turns into  $\$  after the unescaping of the back-slashes.

Note the \_O\_BINARY flag, which tells Windows to treat the stream as non-text data. In the absence of this flag, Windows will convert newline characters and treat CTRL-Z (0x1a) as EOF (end of file).

A "Device or resource busy" (errno = EBUSY) error will be issued if the device file is already opened for read by another process (non-exclusive file opening is available on request). If "No such device" (errno = ENODEV) occurs, it's most likely an attempt to open a write-only stream.

With the file opened successfully and buf pointing at an allocated buffer in memory, data is read with:

while (1) {

rc = \_read(fd, buf, numbytes);

numbytes is the maximal number of bytes to read.

The returned value, rc, contains the number of bytes actually read (or a negative value if the function call completed abnormally).

Note that \_read() always returns immediately if the amount of data that was requested in numbytes is available. Otherwise, it will return after about 10 ms if there is any data available. If no data at all is available, \_read() sleeps until it can return with data.

The driver checks the availability of data in the sense that the IP core has received that data from the application logic in the FPGA. The mechanism of DMA buffers is transparent to the caller of the function  $\_$ read(), and never delays the delivery of data to the  $\_$ read() function call because a DMA buffer isn't full, as explained in section A.3.5 of the Appendix.

#### **IMPORTANT:**

There is no guarantee that all requested bytes were read from the file, even on a successful return of \_read(). It's the caller's responsibility to make another function call to \_read(), if the completed amount of data was unsatisfactory.

The function call to \_read() should be followed by checking its return value as shown below ("continue" and "break" statements assume a while-loop context):

```

if ((rc < 0) && (errno == EINTR))

continue;

if (rc < 0) {

perror("read() failed");

break;

}

if (rc == 0) {

fprintf(stderr, "Reached read EOF.\n");

break;

}

// do something with "rc" bytes of data</pre>

```

The first if-statement checks if \_read() returned prematurely because of a signal. This is a result of the process receiving a signal from the operating system.

This is not an error really, but a condition that forces the driver to return control to the application immediately. The use of the EINTR error number is just a way to tell the function's caller that there was no data read. The program responds with a "continue" statement, resulting in a renewed attempt to call the function  $\_$ read() with the same parameters.

If there is some data in the buffer when the signal arrives, the driver will return the number of bytes already read in rc. The application will not know that a signal has arrived, and according to UNIX programming convention, it has no reason to care: If the signal requires action (e.g. SIGINT resulting from a CTRL-C on keyboard), the responsibility for this action is either on the operating system, or a registered signal handler.

Note that some signals shouldn't have any effect on the execution flow, so if signals aren't detected as shown above, the program may suddenly report an error for no apparent reason.

Handling the EINTR scenario is also necessary to allow the process to be stopped (as with CTRL-Z) and resumed properly.

Note that signals belong to the world of UNIX, so despite all that is said about them above, it's not clear if they will arrive at all on a Windows computer. Either way, the

related if-statement is useless but harmless at worst.

The second if-statement terminates the loop if a real error has occurred after reporting a user-readable error message.

The third if-statement detects if end of file has been reached, which is indicated by a return value of zero. When reading from a Xillybus device file, the only reason for this to happen is that the application logic has raised the stream's \_eof pin (which is part of the IP core's interface on the FPGA).

## 3.3 Guidelines for writing data

Assuming that the variables have been declared as follows:

int fd, rc; unsigned char \*buf;

The device file is opened with the low-level \_open (the file descriptor is in integer format):

```

fd = _open("\\\.\\xillybus_ourdevice", O_WRONLY | _O_BINARY);

if (fd < 0) {

perror("Failed to open devfile");

exit(1);</pre>

```

The prefix in the file name turns into  $\$  after the unescaping of the backslashes.

Note the \_O\_BINARY flag, which tells Windows to treat the stream as non-text data. In the absence of this flag, Windows will convert newline characters and treat CTRL-Z (0x1a) as EOF (end of file).

A "Device or resource busy" (errno = EBUSY) error will be issued if the device file is already opened for write by another process (non-exclusive file opening is available on request). If "No such device" (errno = ENODEV) occurs, it's most likely an attempt to open a read-only stream.

With the file opened successfully and buf pointing at an allocated buffer in memory, data is written with:

while (1) {

rc = \_write(fd, buf, numbytes);

numbytes is the maximal number of bytes to be written.

The returned value, rc, contains the number of bytes actually written (or a negative value if the function call completed abnormally).

#### **IMPORTANT:**

There is no guarantee that all requested bytes were written to the file, even on a successful return of \_write(). It's the caller's responsibility to make another function call to \_write() if the completed amount of data was unsatisfactory.

The function call to \_write() should be followed by checking its return value as shown below ("continue" and "break" statements assume a while-loop context):

```

if ((rc < 0) && (errno == EINTR))

continue;

if (rc < 0) {

perror("write() failed");

break;

}

if (rc == 0) {

fprintf(stderr, "Reached write EOF (?!)\n");

break;

}

// do something with "rc" bytes of data</pre>

```

The first if-statement checks if \_write() returned prematurely because of a signal. This is a result of the process receiving a signal from the operating system.

This is not an error really, but a condition that forces the driver to return control to the application immediately. The use of the EINTR error number is just a way to tell the function's caller that there was no data written. The program responds with a "continue" statement, resulting in a renewed attempt to call the function \_write() with the same parameters.

If some data was written before the signal arrived, the driver will return the number of bytes already written in rc. The application will not know that a signal has arrived, and according to UNIX programming convention, it has no reason to care: If the signal requires action (e.g. SIGINT resulting from a CTRL-C on keyboard), the responsibility for this action is either on the operating system, or a registered signal handler.

Note that some signals shouldn't have any effect on the execution flow, so if signals

aren't detected as shown above, the program may suddenly report an error for no apparent reason.

Handling the EINTR scenario is also necessary to allow the process to be stopped (as with CTRL-Z) and resumed properly.

Note that signals belong to the world of UNIX, so despite all that is said about them above, it's not clear if they will arrive at all on a Windows computer. Either way, the related if-statement is useless but harmless at worst.

The second if-statement terminates the loop if a real error has occurred after reporting a user-writable error message.

The third if-statement detects if the end of file has been reached, which is indicated by a return value of zero. When writing to a Xillybus device file, this should never happen.

## 3.4 Performing flush on asynchronous downstreams

As mentioned in paragraph 2.4, data written to an asynchronous stream on a PCIe / AXI IP core is not necessarily sent immediately to the FPGA, unless a DMA buffer is full (there are several DMA buffers). This behavior improves performance by making sure that the allocated buffer space is utilized. This also improves the efficiency of the packets sent on the PCIe / AXI bus.

As also mentioned already, XillyUSB IP cores send the data virtually right away, even when the stream is asynchronous, as there's an efficient arrangement for that with the USB interface. Performing flush has therefore a significance with XillyUSB IP cores only when it involves waiting for the transmission to complete.

Streams to the FPGA undergo a flush automatically when closing the file descriptor, however this is a best-effort mechanism that can't be relied upon. The function call to \_close() is delayed until all data has arrived at the FPGA in a manner similar to the way write() function calls are delayed on synchronous streams. The significant difference is that \_close() waits up to one second for the flush to complete. If the flush isn't completed by then, \_close() returns anyhow, and issues a warning message in the Event Log. Note however that in some rare scenarios, the last few words of remaining data may be lost without any warning while closing a file descriptor.

It's also possible to request a flush of an asynchronous stream explicitly, by calling the function \_write() with a buffer that has a length of zero, i.e.

```

while (1) {

rc = _write(fd, NULL, 0);

if ((rc < 0) && (errno == EINTR))

continue; // Interrupted. Try again.

if (rc < 0) {

perror("flushing failed");

break;

}

break; // Flush successful

}</pre>

```

Please note the following:

- There is no clear system definition for what a \_write() function call should do when the count is zero, leaving the choice to each device driver. This method for flushing is specific to Xillybus.

- Unlike \_close(), a \_write() as shown above returns immediately, regardless of when the data is consumed on the FPGA.

- Because of this, this kind of \_write() is pointless with XillyUSB. It has nothing to do, and indeed does nothing: The data is sent virtually immediately anyhow, and the \_write() function call wouldn't wait in any case.

- Since no data is read from the buffer, the buffer argument in the \_write() function call can take any value, including NULL, as demonstrated above.

- Using higher-level API, with a buffer with zero length, may not have any effect at all. For example, calling the function fwrite() to write zero bytes may simply return with nothing done, since what this function usually does is adding the data to a buffer created by the C run-time library.

- fflush() is irrelevant: It performs a flush of the higher-level buffer, but doesn't send a flush command to the low-level driver.

- There is no need perform a flush on streams in the other direction (from FPGA to host), and there's no way to do so. This is because a flush of such streams is automatically performed when a host's attempt to read data is about to put the process to sleep (i.e. block).

### 3.5 Using Microsoft's native API

Although it's not recommended for use, an example of reading from a stream with Microsoft's native API is given for the sake of completeness. The full code is available as winstreamread.c in the demo application bundle (see Getting started with Xillybus on a Windows host).

First, let's define a helper function for printing out errors. It's the counterpart of perror() for Windows: Its purpose is to turn an error code into a message, that is readable by a human.

It accepts a string for a description of the attempted action, and the error code. In response, the function prints the given string, the error code and the human-readable error description as translated by Windows.

```

void errorprint(char *what, DWORD dw) {

LPVOID lpMsgBuf;

FormatMessage(

FORMAT_MESSAGE_ALLOCATE_BUFFER |

FORMAT_MESSAGE_FROM_SYSTEM |

FORMAT_MESSAGE_IGNORE_INSERTS,

NULL,

dw,

MAKELANGID(LANG_NEUTRAL, SUBLANG_DEFAULT),

(LPTSTR) &lpMsgBuf,

0, NULL );

fprintf(stderr, "%s: Error=%08x:\n%s\n",

what, dw, lpMsgBuf);

LocalFree(lpMsgBuf);

}

```

The following variable declarations are assumed:

HANDLE fh; DWORD rc;

A file is opened with a function call to CreateFile(), which despite its name doesn't necessarily create a file, but opens it.

```

fh = CreateFile("\\\\.\\xillybus_ourdevice", // file to open

GENERIC_READ, // open for reading

0, // do not share

NULL, // no security

OPEN_EXISTING, // existing file only

FILE_ATTRIBUTE_NORMAL,

NULL); // no attr. template

```

CreateFile() always opens the file in "binary mode". As a matter of fact, it doesn't support the LF conversion known as "text mode".

The prefix in the file name turns into  $\$  after the unescaping of the backslashes.

The success of opening the file is checked, and the function errorprint() (defined above) is called in case of a failure.

```

if (fh == INVALID_HANDLE_VALUE) {

errorprint("Failed to open file", GetLastError());

return 1;

}

```

With the file opened successfully and buf pointing at an allocated buffer in memory, data is read with:

```

if (!ReadFile(fh, buf, numbytes, &rc, NULL)) {

errorprint("ReadFile", GetLastError());

return 1;

}

```

numbytes is the maximal number of bytes to read.

rc, which is written to by ReadFile(), contains the number of bytes actually read.

If it's zero, the end of file has been reached. When reading from a Xillybus device file, the only reason for this to happen is that the application logic has raised the stream's \_eof pin (which is part of the IP core's interface on the FPGA).

```

if (rc == 0) {

fprintf(stderr, "Reached EOF.\n");

return 0;

```

Xillybus host application programming guide for Windows

### **IMPORTANT:**

There is no guarantee that all requested bytes were read from the file, even on a successful return of ReadFile(). It's the caller's responsibility to call the function ReadFile() again if the completed amount of data was unsatisfactory.

# 3.6 Monitoring the amount of data in driver's buffers

This topic is discussed in Xillybus FPGA designer's guide, in the section named "Monitoring the amount of buffered data".

# 3.7 XillyUSB: The need to monitor the quality of the physical data link

Unlike PCIe, the physical data link that is used with USB 3.0 has been observed generating bit errors. This is uncommon, and indicates a problem with one of the involved components, most likely the host's USB port or the cable.

The USB protocol provides a variety of mechanisms for overcoming bit errors when such occur, however the random nature of these errors puts the link protocol in states that are rarely reached. As a result, this may reveal bugs in the host's USB controller. Such bugs, to the extent that they exist, are normally hidden, and cause a variety of weird behaviors.

Hence if the physical data link suffers from frequent bit errors, there's a significant risk that the USB connection will become stuck, spontaneously disconnected, or in rare cases, even cause errors in the application data.

XillyUSB provides a means for monitoring the health of the physical data link, by virtue of a dedicated device file, \\.\xillyusb\\_NN\\_diagnostics. The show-diagnostics utility (explained on this web page) exposes the information collected on this matter.

It's highly recommended that applications based upon XillyUSB continuously monitor the first five counters that are displayed by the showdiagnostics utility (relating to bad packets, errors detected and Recovery requests), and ensure that they don't increase. If they do so, and in particular if they increase repeatedly, the application software should suggest corrective actions, possibly one of the following:

• Disconnect and reconnect the USB plug to another port. This may help, because some motherboards have different ports connected to different brands of USB host controllers (usually to support later versions of the USB 3.x protocol).

- Disconnect and reconnect the USB plug on the same port. This might help if the analog signal equalizer (which cancels attenuations and reflections caused the physical signal path) ends up in a suboptimal state.

- Attempt using a different USB cable.

It's quite likely that an application continues to work flawlessly even in the presence of bit errors. The suggestion for corrective actions is therefore best done while taking into account that the user probably doesn't experience any visible problem.

The showdiagnotics.pl utility can be used as reference code, as its C source code is published in the same zip file as the executable.

Note that none of these problems is specific to XillyUSB. Rather, these issues are as likely to affect any USB 3.0 device, however XillyUSB offers means to detect them. Also, it's worth reiterating that PCIe links are not known to suffer from any similar issues, most likely due to the better controlled physical connections and signal routings.

# 4

# Continuous I/O at high rate

# 4.1 The basics

There are four practices that are nearly essential to achieve a high-rate continuous data flow between the host and the FPGA:

- Using asynchronous streams

- Making sure the driver's buffers are large enough to compensate for time gaps between the I/O operations of the user space application.

- Having the user space application read data from the device file as soon as there is data available, or write data to it as soon as there is space available in the buffers.

- Never closing and reopening the device files while the FPGA keeps inserting or draining data.

XillyUSB presents additional challenges with maintaining a continuous flow of data, as explained on this web page.

Monitoring how much data is held in the driver's buffers at any given time is discussed in Xillybus FPGA designer's guide, in the section named "Monitoring the amount of buffered data".

The first item in the list above, of using asynchronous streams, is discussed in section 2. The second and third are discussed in the remainder of this section.

To understand the the fourth item, recall that the advantage of asynchronous streams is that data runs between the FPGA and host without the intervention of the user space application. This flow is stopped when the file is closed.

Specifically for a stream from the host to the FPGA, closing the file forces a flush of all data in the buffers, and the file is closed only after that is finished (or after one second). As a result, there is a time gap with no data flow from the moment that the file is closed, to when the file is open again (and data is written to the file descriptor).

As for streams from the FPGA, closing the file leads to loss of any data in the pipe that goes from the application logic in the FPGA, to the user space application in the host (i.e. the FPGA's FIFO and driver's buffers). The only way to avoid this loss is draining all data from this pipe before closing the file. Once again, there's a time gap with no data flowing, between closing the file and opening it again.

A common mistake is to use the EOF capability to mark data chunks (e.g. complete video frames), and by doing so, forcing the host to close and reopen the device file at known boundaries. However this significantly increases the risk for an overflow at the FPGA's FIFO.

It's important to keep in mind that the operating system may take away the CPU from a user space application at any given moment (preemption), so time gaps of several, and sometimes tens of milliseconds can occur between subsequent function calls in a program.

## 4.2 Large driver's buffers

One of the greatest challenges in transferring data at a high rate between the FPGA and host is to maintain a continuous flow. In applications involving data acquisition and playback, an overflow or shortage of data renders the system nonfunctional. To avoid this, the driver allocates large RAM buffers on the host for its own use. These buffers compensate for the gaps in time, during which the application isn't available to handle data transfers.

Xillybus allows allocation of huge driver's buffers, but this memory must be allocated from the pool of the operating system's kernel RAM. On some systems (32-bit systems in particular) the addressing space of such memory is limited to 1 GB by the Windows operating system, even if the total RAM available is significantly larger. In systems with RAM of less than 1 GB, all memory may be used for driver's buffers.

Much larger buffers can be allocated on 64-bit systems when using an enhanced host driver, as discussed on this page:

#### http://xillybus.com/doc/huge-dma-buffers/

Except for with XillyUSB, the driver's buffers are allocated when the Xillybus driver is loaded (typically early in the boot process) and is freed only when the driver is

unloaded from the kernel (usually during system shutdown). When the buffers are huge, this usually means that a significant part of the kernel's RAM pool is occupied by the driver's buffers. It's a fairly reasonable setting, since the application using these buffers is likely to be the main purpose of the machine it's running on.

A potential problem with huge buffers is that hey occupy contiguous segments of physical RAM. This is contrary to a buffer allocated in a userspace program, which is contiguous in virtual address space, but can be spread all over the physical memory, or even not occupy any physical RAM at all.

The pool of available memory becomes fragmented as the operating systems runs. This is why the Xillybus driver allocates its buffers as soon as possible, and retains them even when not actively used. Attempting to unload the driver and reload it at a later stage may fail for the same reason.

XillyUSB has a different approach to memory allocation, which is more tolerant to physical memory fragmentation. This is one of the reasons that its driver allocates RAM for its buffers when a device file is opened, and releases it when the file is closed.

Precautions should however be taken to avoid a shortage of kernel RAM. The IP Core Factory's automatic memory allocation ("autoset internals") algorithm is designed not to consume more than 50% of the relevant memory pool, i.e. 512 MB, based upon the assumption that a modern PC has more than 1 GB of RAM installed. It's probably safe to go as high as 75% as well, which can be done by setting the buffer sizes manually.

Overallocation of buffers may lead to system instability. In particular, the operating system is likely to kill processes apparently randomly, whenever it fails to allocate RAM from the kernel pool.

#### 4.3 RAM buffers in user space

For applications that require buffers larger than 512 MB on a 32-bit machine, it's recommended to do some of the buffering in user space RAM. On 64-bit machines, this option is rarely relevant, except for when the desired buffer size is very large, and not a power of 2 ( $2^N$ ). For example, supplying a buffer of 62 GB for a stream is not possible by virtue of Xillybus DMA buffers, but can be achieved with user space RAM.

It may seem counterintuitive that the problem of I/O continuity can be solved by allocating a huge buffer in the user space application. Indeed, this solution doesn't help when the operating system starves the application of CPU time. But if the operating system's scheduler is fairly well designed and the priorities are set right, a user space application will get its CPU slice often enough, even on a computer that is under heavy load.

It's important to pay attention to the first fill of the buffer: Modern operating systems don't allocate any physical RAM when a user space application requests memory. Instead, they just set up the memory page tables to reflect the memory allocation. Actual physical memory is allocated only when the application attempts to use it. This is a brilliant method for saving resources, but can have a disastrous impact on a data acquisition application: For example, consider what happens when data begins to rush in from a data source. The application writes the data to the buffer just allocated, but each time a new memory page is accessed, the operating system needs to get a new physical memory page. If there happens to be free physical RAM, or if there is a quick way to release physical memory (e.g. disk buffers which are already in sync with the disk), this memory juggling can go by unnoticed. But in the absence of immediate sources of physical RAM, disk operations may have to take place (RAM swapping to disk or flushing disk buffers), which can halt the application for too long.

The really bad news is that the ability to take the initial load of data depends on the overall system's state. Hence a program that usually works may suddenly fail, because some other program just did something data intensive on the same computer.

The natural solution is memory locking: VirtualLock() tells the operating system that a certain chunk of (virtual) memory must be held in physical RAM. This forces allocation of physical memory immediately, so if disk operations are needed to complete the function call, it may take some time to return.

The operating system is reluctant to lock large chunks of RAM, as this impacts its overall performance. Calling the function SetProcessWorkingSetSize() to raise the RAM locking limit is often necessary for VirtualLock() to succeed.

# 4.4 Why not just Windows pipes?

The Windows standard API supports (at least) two functions for creating pipes: CreatePipe() and CreateNamedPipe(). These two functions allow the caller to determine the size of the buffer, so on the face of it, they could do the job. Unfortunately, Windows considers the requested buffer size as a suggestion, as stated in the web pages for CreatePipe() and CreateNamedPipe().

# 4.5 Overview of the fifo.c demo application

Among the demo applications, which can be downloaded for Linux and Windows, there's one called "fifo.c". It's an example of how to implement a RAM FIFO using two threads, which has been tested on 32-bit and 64-bit platforms.

For more about the demo applications, see Getting started with Xillybus on a Windows host.

Note that unlike everywhere else in the documentation, the word "FIFO" in this section refers to a RAM buffer on the host, and not the FIFO in the FPGA.

The purpose of this program is to test fast streams, where a RAM FIFO is necessary to maintain a huge RAM buffer. In other words, if you need a buffer smaller than say, 16 GB, odds are that you don't need this program.

It can also be used a basis for modification and adoption in custom applications. It's designed with no mutexes, so no thread ever goes to sleep just because another thread holds the lock. Sleeping (blocking) does occur, of course, when the FIFO's state requires that (e.g. a read is requested from an empty FIFO).

This implementation without mutexes requires careful use of the API functions, as they're not reentrant. This is however no problem with one thread for reading, and one thread for writing.

To run it for data acquisition from a device file into a disk file with a buffer of 128 MB, type something like:

#### > fifo 134217728 \\.\xillybus\_async > dumpfile

If no file name is given as the second argument, the program reads from standard input.

The program creates three threads:

- read\_thread() reads from standard input (or the file given in the command line) and writes the data into the FIFO

- write\_thread() reads from the FIFO and writes to standard output

- status\_thread() prints a status line to standard error recurrently

The third thread has no functional significance, and can be eliminated. It's also possible to have one of the read/write functionalities running in the main thread. For example, in a data acquisition application, it may be natural to launch only read\_thread() to

move data from the file descriptor to the FIFO, but consume the data from the FIFO in the thread of the main application.

## 4.6 fifo.c modification notes

If you want to modify the program, here are a few things to keep in mind:

- The fifo\_\* functions are not reentrant. It's safe to use them when each thread uses a set of functions that no other thread uses (which is a natural use).

- The function fifo\_init() can take time to return, and should be called before an asynchronous Xillybus device file is opened.

- The thread that reads and the thread that writes in the applications always attempt the maximal number of bytes allowed in their I/O requests. This can be problematic in some cases, e.g. when the I/O source is /dev/zero and the destination is /dev/null. Both will complete the entire request in one attempt, so the FIFO will go from completely empty to completely full and over again. In such cases, it's more sensible to limit the requested number of bytes in calls to I/O functions.

# 4.7 RAM FIFO functions

Except for modifying the fifo.c example, it's possible to adopt a group of functions from the source code.

A section of FIFO API functions is clearly distinct in the fifo.c file. These functions can be used in custom applications, by following the example and according to the functions' description below.

#### **IMPORTANT:**

Even though the fifo\_\* functions are intended for use in a multi-threaded environment, these functions are **not reentrant**. This means that one thread should call functions related to reading from the FIFO, and another thread should do writes, so each thread calls its separate set of functions.

Except for an initializer, destroyer and a thread join helper, the API has four functions for reading and writing, two for each direction. Neither of these functions actually access the data in the FIFO; they merely maintain the FIFO's state and supply the information necessary to perform reads, writes, memory copies etc.

The intended execution procedure is as follows: The thread that reads from the FIFO calls the function fifo\_request\_drain(), which returns information about how many bytes can be read, and a pointer from which data can be read. If the FIFO is empty, the thread will sleep until data arrives.

The user application then makes whatever use it needs with the data pointed to. After finishing to consume some or all of the data (write to a file, copy data, run some algorithm etc.), it calls the function fifo\_drained() to inform the FIFO API how many bytes were actually consumed. The API releases the relevant portion of memory in the FIFO. If the thread that writes was sleeping because the FIFO was full, it is woken up.

Note that the thread that reads doesn't ask for a specific number of bytes. Rather, fifo\_request\_drain() tells the application how many bytes can be consumed, and the application reports back how many it chose to consume in fifo\_drained().

As for the opposite direction, a similar approach is taken: The thread that writes calls the function fifo\_request\_write(). This function returns the number of bytes that can be written to the FIFO, or sleeps if the FIFO is full. The user application writes as many bytes it needs (but not more than fifo\_request\_write() allowed it to) to the address it got from fifo\_request\_write() and then reports back what it did to fifo\_wrote().

We'll now go through each of these functions in detail.

#### 4.7.1 fifo\_init()

fifo\_init(struct xillyfifo \*fifo, unsigned int size) – This function initializes the FIFO's information structure and allocates memory for the FIFO as well. It also attempts to lock the FIFO's virtual memory to physical RAM, making it ready for immediate fast writing and preventing it from being swapped to disk.

fifo\_init() allocates memory for a buffer of size bytes. size can be any integer (i.e. doesn't have to be a power of 2,  $2^N$ ) but a multiple of what the system considers int is recommended.

Note that this function can take several seconds to return: The request for a large portion of physical RAM may force the operating system to swap other processes' RAM pages to disk, or force disk cache flushing. In both cases, fifo\_init() may have to wait for a lot of data to be written to disk before returning.

The function returns zero on success, nonzero otherwise.

#### 4.7.2 fifo\_destroy()

fifo\_destroy(struct xillyfifo \*fifo) – Frees the FIFO's memory after unlocking it, and releases thread synchronization resources. This function **should** be called when the main program exits, because even though the thread synchronization resources are released automatically in current implementations of Windows, their API doesn't guarantee this.

This function is of void type (hence returns nothing).

#### 4.7.3 fifo\_request\_drain()

fifo\_request\_drain(struct xillyfifo \*fifo, struct xillyinfo \*info) – Supplies a pointer to read data from the FIFO as info->addr, and informs how many bytes can be read, beginning from that pointer, in info->bytes.

The info structure must **not** be the same one that is used for function calls to fifo\_request\_write(). Each thread should maintain a local variable of its own for this structure.

#### **IMPORTANT:**

The number of bytes returned does **not** indicate how much data is left for reading in the FIFO: It may also reflect the number of bytes left until the end of the FIFO's memory buffer. Hence a significantly lower number is possible when the pointer comes close to the end of the buffer.

The function also sets fifo->position to indicate the FIFO's current read position as a value between 0 and size-1, where size is the value that was given to fifo\_init(). A nonzero fifo->slept indicates that the FIFO was empty upon invocation.

The function returns the number of bytes allowed for read (same as info->taken). But if the function fifo\_done() has been called, and the FIFO is empty, fifo\_request\_drain() returns zero.

#### 4.7.4 fifo\_drained()

fifo\_drained(struct xillyfifo \*fifo, unsigned int req\_bytes) – This function changes the FIFO's state to reflect the consumption of req\_bytes bytes. If fifo\_request\_write() was sleeping because the FIFO was full, it will be woken up.

#### **IMPORTANT:**

There is **no sanity check** on req\_bytes. It's the user application's responsibility to make sure that req\_bytes is not larger than info->bytes returned by the last function call to fifo\_request\_drain().

This function is of void type (hence returns nothing).

#### 4.7.5 fifo\_request\_write()

fifo\_request\_write(struct xillyfifo \*fifo, struct xillyinfo \*info) – Supplies a pointer to write data to the FIFO as info->addr, and informs how many bytes can be written, beginning from that pointer, in info->bytes.

The info structure must **not** be the same one that is used for function calls to fifo\_request\_drain(). Each thread should maintain a local variable of its own for this structure.

#### **IMPORTANT:**

The number of bytes returned does **not** indicate how much data is left for writing in the FIFO: It may also reflect the number of bytes left until the end of the FIFO's memory buffer. Hence a significantly lower number is possible when the pointer comes close to the end of the buffer.

The function also sets fifo->position to indicate the FIFO's current write position as a value between 0 and size-1, where size is the value that was given to fifo\_init(). A nonzero fifo->slept indicates that the FIFO was full upon invocation.

The function returns the number of bytes allowed for write (same as info->taken). But if the function fifo\_done() has been called, fifo\_request\_write() returns zero, even if the FIFO is not full (there is no point writing data into a FIFO that will never be read).

### 4.7.6 fifo\_wrote()

fifo\_wrote(struct xillyfifo \*fifo, unsigned int req\_bytes) – This function changes the FIFO's state to reflect the insertion of req\_bytes bytes. If fifo\_request\_drain() was sleeping because the FIFO was empty, it will be woken up.

#### **IMPORTANT:**

There is **no sanity check** on req\_bytes. It's the user application's responsibility to make sure that req\_bytes is not larger than info->bytes returned by the last function call to fifo\_request\_write().

This function is of void type (hence returns nothing).

#### 4.7.7 fifo\_done()

fifo\_done(struct xillyfifo \*fifo) – This function is optional for use, and helps the application to quit gracefully if either of the threads (reading or writing) has finished. It merely sets a flag in the FIFO's structure and wakes up both threads if they were sleeping. By doing so, the fifo\_request\_drain() will return zero rather than sleeping if the FIFO is empty, and fifo\_request\_write() will return zero regardless.

This way, the callers of these functions know that the FIFO has no more use, and may act as necessary, which is most likely to stop the execution of the thread.

Call this function when the data source feeding the pipe has ended (e.g. EOF reached) or when the data comsumer is no longer receptive (e.g. a broken pipe).

This function is of void type (hence returns nothing).

#### 4.7.8 The FIFO\_BACKOFF define variable

Sometimes it's not desirable to let the FIFO get full to the last byte. Even though there is no apparent reason avoiding that, it may be desirable to maintain a small gap between where data is written to and where its read from.

For example, FIFO\_BACKOFF can be set to 8, so the last byte written to the FIFO never shares a 64-bit word with the first valid byte for read. This is a rather far-fetched precaution, but comes at the low price of 8 bytes of memory.

There is no need for this feature when working with Xillybus or XillyUSB.

# 5

# **Cyclic frame buffers**

# 5.1 Introduction

In some applications, in particular real-time processing of video images, it's often desired to maintain a number of buffers, so that each buffer has a fixed size. In a video processing application, each such buffer contains one frame. This allows skipping frames or replaying them more than once, as necessary.

In a frame grabber application, an overflow condition can be handled by skipping one or more frames until there is a vacant buffer. For example, in a live view application, such overflow condition may occur when the viewing window is moved or resized. Dropping frames like this prevents the disruption of the continuous data flow from the video source, while maintaining a small latency.

In a frame replay application (e.g. a screen showing live output), the output image is repeated when there is no newer frame to display. This resolves situations where the source (e.g. a disk) momentarily stalls, causing the displayed image to freeze for a short while. While not completely graceful, it's better than having the stream going out of sync. In many cases, the image repetition mechanism, although somewhat crude, works well for overcoming differences in frame rates, in particular when the output's frame rate is considerably higher than the input's frame rate (e.g. 30 fps to 60 fps).

This section discusses how the FIFO demo application, which was introduced in paragraph 4.5, can be modified to manage a set of buffers of this sort.

# 5.2 Adapting the FIFO example code

There are similarities between maintaining a cyclic set of frame buffers and a FIFO. In fact, if each byte in the FIFO represents a frame buffer, the readiness to read or

write a certain byte in the FIFO is equivalent to the readiness to read or write an entire frame buffer.

For example, suppose a frame grabber application, where four frame buffers are allocated for containing the received image data. Suppose further that a FIFO of four bytes is set up to help managing these four frame buffers as follows:

The thread receiving the data starts from the first frame buffer, and continues to the next ones in a cyclic manner. Before starting to write to a new frame buffer, this thread checks that the four-byte FIFO isn't full. After it has completed a frame buffer, it writes a byte into the FIFO and goes to the next one if the FIFO isn't full.

The thread consuming the image data cycles through the frame buffer in the same order. Before attempting to read from a new frame buffer, it checks that the four-byte FIFO isn't empty. When it has finished with a frame buffer and is ready to go to the next, it reads a byte from the FIFO.

By sticking to this convention, it's guaranteed that the thread receiving the data will never overrun a frame buffer that hasn't been consumed, and that the consuming thread will never attempt to read from a frame buffer that contains invalid data. As a matter of fact, the number of bytes in the FIFO represents the number of valid frame buffers in the set.

Note that the values of the bytes written and read make no difference, so there's no actual need to allocate these four bytes of memory and store data in them. Only the FIFO's handshake mechanism plays a role.

Hence, the FIFO API outlined in paragraph 4.7 can be adopted as is:

- Call the function fifo\_init() with the size parameter as the number of frame buffers (recall that size can be any integer). fifo\_init() will allocate and lock memory for the FIFO, which will never be used (since each bytes just symbolizes a frame buffer). This waste of memory is negligible, but the relevant portions in the code can be removed to avoid future confusion.

- Call the function fifo\_request\_drain() to get a frame buffer to read from. info->position will contain the index to the frame buffer to use (numbering starts at 0). If no frame buffer is ready, fifo\_request\_drain() will sleep until there is.

- After reading from the buffer, call the function fifo\_drained() with bytes\_req=1.

- The functions fifo\_request\_write() and fifo\_wrote() are called in the same way by the thread writing to the frame buffers.

• FIFO\_BACKOFF should be set to zero. There is no point for this feature with frame buffers.

# 5.3 Dropping and repeating frames

Let's take the case of a continuous source of image frames which must never reach the state of overflow, given that the data comsumer may not always collect the data fast enough.

The idea is to prevent blocking on the thread, which transports data from the data source to the frame buffers. To achieve this, the following sequence should be looped on for each incoming frame:

- Call the function fifo\_request\_write() to find out which frame buffer to write to

- Write to the frame buffer pointed at by info->position

- When done writing, call the function fifo\_request\_write() again. This function call will surely not sleep (block), because no buffer has been reported as written to, since the previous call.

- If fifo\_request\_write() just returned a value larger than 1, call the function fifo\_wrote() (with req\_bytes=1, of course). A subsequent function call to fifo\_request\_write() will surely not sleep (block), because there were more than one buffer to spare, and only one was consumed. In fact, the next function call to fifo\_request\_write() can be substituted by just picking the next frame buffer.

- On the other hand, if fifo\_request\_write() returns just 1, don't call the function fifo\_wrote(). Instead, use the current buffer again on the next loop executing for accepting incoming data, or just drain a whole frame from the data source to no particular destination.

Since this usage prevents blocking, it's possible to delete the while() loop in the implementation of fifo\_request\_write(), as it is never invoked. Further code reduction is possible by removing the relevant event, as well as its initialization and destruction code. Leaving them in the code has a minimal effect, so this optimization is a mostly a matter of keeping the code readable.

A similar approach can be taken to repeat frames on the thread writing from the FIFO: Call the function fifo\_request\_drain() again just before calling the function fifo\_drained(), and repeat the current frame if it returns less than 2.

# 6

# Specific programming techniques

## 6.1 Seekable streams

A synchronous Xillybus stream can be configured to be seekable. The stream's position is presented to the application logic in the FPGA in separate wires as an address, so interfacing memory arrays or registers in the FPGA is straightforward, as shown in the demo bundle and example code.

This feature is useful in particular for setting up control registers in the FPGA. The synchronous nature of the stream ensures that the register in the FPGA is set before the low-level I/O function returns.

The following code snippet demonstrates how to write len bytes of data to address address in the memory or register space in the FPGA, assuming that these two variables are previously set.

```

int rc, sent;

if (_lseek(fd, address, SEEK_SET) < 0) {

perror("Failed to seek");

exit(1);

}

for (sent = 0; sent < len;) {

rc = _write(fd, buf + sent, len - sent);

if ((rc < 0) && (errno == EINTR))

continue;

if (rc <= 0) {

perror("Failed to write");

exit(1);

}

sent += rc;

}</pre>

```

fd is also assumed to be the value returned from a function call to  $\_open()$ , where the file was opened for write or read-write, and buf pointing to the buffer containing data to be written.

This example is an extension of the example shown in paragraph 3.3.

The only special thing in this code is the function call to \_lseek(), which sets the address. Only the SEEK\_SET option should be used as the third argument, when calling the \_lseek() function.

Subsequent function calls update the address in accordance with the I/O stream's position, so there is no limitation on making multiple sequential writes after calling the function \_lseek().

For streams which are accessed as 16-bit or 32-bit words in the FPGA, the address given to Iseek() must be a multiple of 2 or 4, respectively. The address presented to the application logic in the FPGA is maintained at all times as the stream's I/O position (initially as given to Iseek()) divided by 2 or 4, respectively. For wider words, the same logarithmic rule applies.